The Cmod, or Carrier Module, family of products is designed to offer quick, simple, and flexible integration of an FPGA into circuit design, prototyping, and learning/hobby projects.

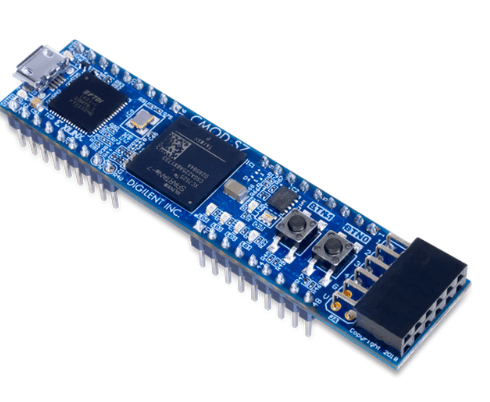

The Digilent Cmod S7 is a small, 48-pin DIP form factor board, populated with 36 pins, built around a Xilinx® Spartan®-7 FPGA that brings FPGA power and prototyping to a solderless breadboard.

The board includes a Quad-SPI flash for programming, as well as a USB-JTAG programming circuit and USB-UART bridge. The Cmod S7 also features a clock source, Pmod port, and onboard I/O with LEDs and pushbuttons. There are 32 FPGA I/O signals, 2 FPGA analog input signals, an external power input rail, and ground that are routed to 100-mil-spaced through-hole pins, making the Cmod S7 compatible with solderless breadboards. This form factor makes the Cmod S7 a great option for flexible and affordable prototyping, or learning FPGA and digital logic circuits. At just .7″ by 3.05″, it can also be loaded in a standard socket and used in embedded systems.

The Spartan-7 FPGA on the Cmod S7 fits performance into a small form-factor packaging. With the MicroBlaze Soft Processor Core from Xilinx, you can create embedded applications with a variety of peripherals, memory, and interfaces.

-

Xilinx Spartan-7 FPGA (XC7S25-1CSGA225C)

-

3,650 slices containing four 6-input LUTs and 8 flip-flops

-

1,620 Kbits of fast block RAM

-

Three clock management tile, each with a phase-locked loop and mixed-mode clock manager

-

80 DSP slices

-

Internal clock speeds exceeding 450 MHz

-

On-chip analog-to-digital converter (XADC)

-

Programmable over JTAG and Quad-SPI Flash

-

-

Memory

-

4 MB Quad-SPI Flash

-

-

Power

-

Powered from USB or 5V external supply connected to DIP pin 24 (micro USB cable NOT included)

-

-

USB

-

USB-JTAG programming circuitry

-

USB-UART bridge

-

-

Push-buttons and LEDs

-

2 Buttons

-

4 LEDs

-

1 RGB LED

-

-

Expansion Connectors

-

1 Pmod connector

-

8 total FPGA I/O

-

-

48-pin DIP form-factor headers

- 36 populated pins

- 32 total FPGA I/O

- 2 Single-ended 0-3.3V analog inputs to XADC

-